シグナルインテグリティが低い7つの理由

1.ライン抵抗の電圧降下の影響-グランドレベル(0レベル)DCによって引き起こされる低レベルの増加

図中の点線は増加の場合です。この増加は、ICの消費電力、ICの密度、給電方法、アース線抵抗(R)、および給電されるアース線の合計電流に関連しています。ΔVグラウンド=ΔI×ΔR

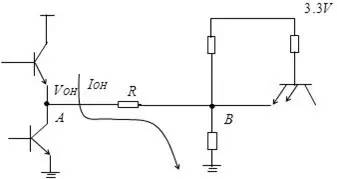

2.信号線抵抗の電圧降下の影響

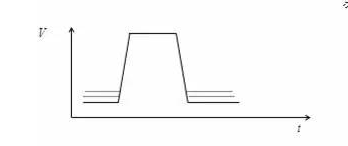

a)IC出力ピンはプリントワイヤまたはケーブルを通って別のICの入力ピンに流れ、出力低レベル電流はプリントワイヤまたはケーブル抵抗の低レベル上昇を引き起こし、その値はΔVOL=IOL×です。 R。図の上の破線を参照してください。

次の図に示すように、明らかに、低レベルの上昇は、印刷されたワイヤの抵抗値と出力低レベル電流に関連しています。

ポイントBの低レベルは、ポイントAの低レベルよりも高くなっています。

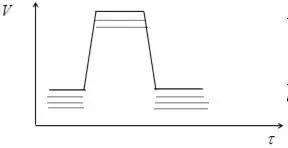

注:IC出力ピンがローレベルの場合、デバイスがドライバではなく一般的なデバイスである場合、出力ローレベル電流がデバイスマニュアルに記載されている値よりもはるかに大きいため、出力トランジスタが終了します。飽和領域と作業に入ります。エリア、出力の低レベルが大幅に上がるように。下の図の上の点線で示されているように:

決定要因:終端方法終端抵抗サイズ出力管飽和深さ出力管β値

b)ICの出力ピンがプリントワイヤまたはケーブルを通過して別のICの入力ピンに到達し、出力の高レベル電流によってプリントワイヤまたはケーブルの抵抗が大幅に減少し、その値はΔVOH=IOH×です。 R、下の画像の高レベルで下の破線を参照してください。

IOHは、次の要因によって決定されます。終端方法、終端レベル、終端抵抗Rは、次の要因によって決定されます。線幅、線の太さ、線の長さは明らかです。高レベルの減少は、印刷された導体の抵抗値に関連します。次の図に示すように、ケーブルと出力の高レベル電流が関連しています。